Dissertation thesis Fully Analog Artificial Neural Network Ing. Filip Paulů

Supervisor doc. Dr. Ing. Jiří Hospodka

Prague, July 2023

### **Declaration**

I hereby declare I have written this doctoral thesis independently and quoted all the sources of information used in accordance with methodological instructions on ethical principles for writing an academic thesis. Moreover, I state that this thesis has neither been submitted nor accepted for any other degree.

In Prague, July 2023

.....

Ing. Filip Paulů

### Acknowledgements

First, I would like to express my gratitude to the Czech Technical University and the Faculty of Electrical Engineering for providing me with the opportunity to pursue my dissertation research.

I would like to express my sincerest thanks to my supervisor doc. Dr. Ing. Jiří Hospodka, for his invaluable guidance, mentorship, and encouragement throughout the entire process. His expertise and dedication helped me to focus on my studies and ensure the success of this project.

I thank my family, and I am grateful for your unwavering support and encouragement during this challenging journey. Your belief in me has been my source of strength and inspiration, for which I am eternally grateful.

Last but not least, I would like to express my appreciation to my fellow students, colleagues, friends, and everyone else who has been a part of this journey, if only by encouraging me or giving me the space for research. Your support and shared knowledge have invaluably helped me overcome challenges and made this experience enriching and enjoyable.

I would also like to thank my English teacher and everyone who has contributed to my understanding and appreciation of the English language. Your collective knowledge, whether shared intentionally or not, has played a crucial role in my ability to write this dissertation. I am truly grateful for the influence you have had on my development as a writer.

Thank you all for your support, encouragement, and contributions that have made this dissertation a reality.

### Abstract

This dissertation introduces the concept of Fully Analog Artificial Neural Networks (FAANNs) capable of processing signals directly from electrical sensors. One of the research motives is to improve measurement accuracy with respect to sensor degradation and changes in environmental conditions. The second motive represents the ability to derive non-measured physical quantities dependent on measured ones, which is especially useful when the quantity is difficult to ascertain, for instance, due to a lengthy and costly chemical process.

Therefore, this work introduces a new design of a fully analog learning process based on the backpropagation algorithm using gradient descent, which remains an open problem. It is a recently discussed problem due to the parallelization of computations which thus increases the learning speed. The proposed structure circumvents the von Neumann bottleneck and avoids limitations associated with sampling, synchronization signals, and clock signal control, enabling real-time learning even for high-speed systems.

The last part of the work focuses on the practical application of FAANNs and thus demonstrates their potential. It is a fully analog adaptive high-frequency filter using the proposed neural networks in combination with a filter bank. Subsequent validation and analysis of the properties of this filter using electrical model behavior simulations explores the effectiveness of real-time adaptation.

**Keywords:** fully analog, neural network, real-time learning, backpropagation, neuromorphic, adaptive filter, analog filter, filter bank, high-speed.

### Abstrakt

Tato disertační práce představuje koncept Plně Analogových Umělých Neuronových Sítí (FAANN), které jsou schopny zpracovávat signály přímo z elektrických senzorů. Jedním z motivů výzkumu je zlepšit přesnost měření s ohledem na degradaci senzorů a změny okolních podmínek. Druhý představuje možnost odvození neměřené fyzikální veličiny, která je závislá na těch měřených, což je obzvláště užitečné, když je velikost požadované veličiny obtížně zjistitelná, například kvůli dlouhému a nákladnému chemickému procesu.

Tato práce proto přichází s novým návrhem plně analogového učícího se procesu založeného na algoritmu zpětného šíření pomocí gradientního sestupu, který stále zůstává otevřeným problémem. Jedná se o problém v poslední době velmi diskutovaný z důvodu paralelizace výpočtů a tím zvýšení rychlosti učení. Navrhovaná struktura obchází von Neumannův bottleneck a také se vyhýbá omezením spojeným se vzorkováním, synchronizačními signály a řízením hodinových signálů, což umožňuje učení v reálném čase i v případě velmi rychlých systémů.

V poslední části se práce zaměřuje na praktické využití FAANN a demonstruje tak jejich potenciál. Jedná se o plně analogový adaptivní vysokofrekvenční filtr využívající navrhovaných neuronových sítí v kombinaci s bankou filtrů. Následná validace a analýza vlastností tohoto filtru pomocí simulací elektrického modelu zkoumá efektivitu adaptace v reálném čase.

**Klíčová slova:** plně analogový, neuronová síť, učení v reálném čase, zpětné šíření, neuromorfní, adaptivní filtr, analogový filtr, banka filtrů, vysokorychlostní.

# Contents

| Al            | bstra | $\mathbf{ct}$                                                 |         | Ι   |

|---------------|-------|---------------------------------------------------------------|---------|-----|

| Co            | onter | ıts                                                           |         | III |

| $\mathbf{Li}$ | st of | figures                                                       | ٦       | VII |

| $\mathbf{Li}$ | st of | tables                                                        |         | XI  |

| $\mathbf{Li}$ | st of | source codes                                                  | Х       | III |

| $\mathbf{Li}$ | st of | acronyms                                                      | -       | XV  |

| 1             | Intr  | oduction                                                      |         | 1   |

| <b>2</b>      | Obj   | ectives of the dissertation                                   |         | 7   |

| 3             | Stat  | te of the art                                                 |         | 9   |

| 4             | Nev   | v structure                                                   |         | 15  |

|               | 4.1   | Blocks                                                        | <br>    | 16  |

|               |       | 4.1.1 Multiplier                                              | <br>    | 16  |

|               |       | 4.1.2 Activation function                                     | <br>    | 16  |

|               |       | 4.1.3 Derivative of an activation function                    |         | 17  |

|               |       | 4.1.4 Subtractor                                              | <br>    | 18  |

|               | 4.2   | Forward propagation structure                                 | <br>    | 18  |

|               | 4.3   | Novel backpropagation structure                               | <br>    | 21  |

|               |       | 4.3.1 Weights implementation                                  |         | 22  |

|               |       | 4.3.2 Error propagation                                       |         | 24  |

|               |       | 4.3.3 Error propagation between layers                        | <br>    | 26  |

|               | 4.4   | Circuit design                                                | <br>    | 28  |

| 5             | Ver   | ification of functionality                                    |         | 31  |

|               | 5.1   | Circuit simulation equipment                                  | <br>••• | 31  |

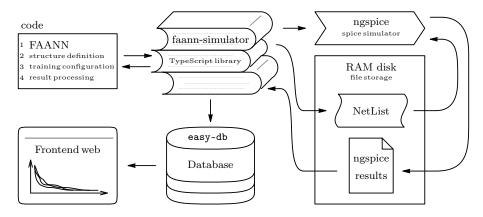

|               |       | 5.1.1 Structure of the faann-simulator $\ldots \ldots \ldots$ | <br>••• | 32  |

|               |       | 5.1.1.1 Application programming interface                     | <br>    | 33  |

|   |            | Contents                                                                                                                                              | ; |

|---|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|   |            |                                                                                                                                                       | c |

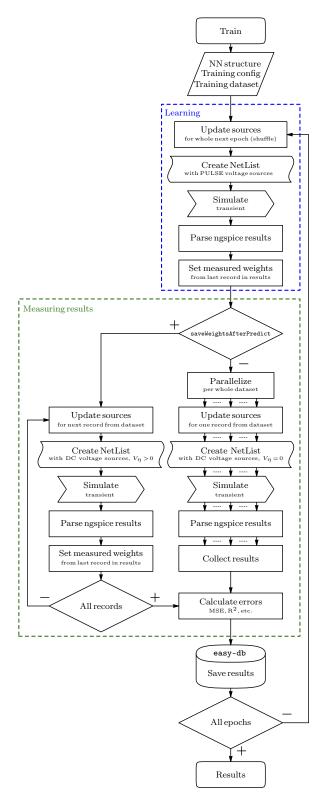

|   | 510        | $5.1.1.2$ Training process $\ldots \ldots \ldots 30$                                                                                                  |   |

|   | 5.1.2      | Outputs                                                                                                                                               |   |

|   |            | rd propagation                                                                                                                                        |   |

|   |            | ng process                                                                                                                                            |   |

|   | 5.3.1      | Weights update analysis                                                                                                                               |   |

|   | 5.3.2      | Learning from dataset                                                                                                                                 |   |

|   | 5.3.3      | Learning multilayer structure                                                                                                                         |   |

|   | 5.3.4      | XOR problem verification                                                                                                                              |   |

|   | 5.3.5      | Dependence on parasitic properties                                                                                                                    |   |

|   | -          | arison with classical ANN                                                                                                                             | 9 |

|   | 5.4.1      | Learning properties                                                                                                                                   | 0 |

|   | 5.4.2      | Learning speed 51                                                                                                                                     | 1 |

| 6 | Adaptive   | frequency filter 53                                                                                                                                   | 3 |

|   |            | sed structure $\ldots \ldots 54$                                                       | 4 |

|   |            | simulator for adaptive frequency filters                                                                                                              |   |

|   | 6.2.1      | Input filters                                                                                                                                         |   |

|   | 6.2.2      | Analog training                                                                                                                                       |   |

|   | 0.2.2      | 6.2.2.1 Input sources                                                                                                                                 |   |

|   |            | 6.2.2.2 Designating a target circuit                                                                                                                  |   |

|   | 6.2.3      | Adaptive frequency filter training                                                                                                                    |   |

|   |            | tion of the adaptive filter concept                                                                                                                   |   |

|   | 6.3.1      | Learning progression over time                                                                                                                        |   |

|   | 6.3.2      | Frequency characteristics                                                                                                                             |   |

|   | 6.3.3      | Filter error measurement                                                                                                                              |   |

|   | 6.3.4      | Total harmonic distortion       66                                                                                                                    |   |

|   |            | ration of adaptive properties                                                                                                                         |   |

|   | 6.4.1      | Dependence on Filter bank                                                                                                                             |   |

|   | 0.4.1      | -                                                                                                                                                     |   |

|   |            |                                                                                                                                                       |   |

|   |            | 1                                                                                                                                                     |   |

|   |            | 6.4.1.3High-order filters716.4.1.4Number of filters in the bank72                                                                                     |   |

|   |            |                                                                                                                                                       |   |

|   | C 4 9      | 6.4.1.5 Adaptation sensitivity to filter inaccuracies 72                                                                                              |   |

|   | 6.4.2      | Dependence on neural network structure $\ldots \ldots \ldots$                                                                                         |   |

|   | -          | ion efficiency $\ldots \ldots \ldots$ |   |

|   | 6.5.1      | Load test                                                                                                                                             | D |

| 7 | Conclusio  | n 75                                                                                                                                                  | 9 |

|   | 7.1 The n  | ew design                                                                                                                                             | 0 |

|   | 7.2 Functi | ionality validation                                                                                                                                   | 0 |

|   | 7.3 Adapt  | ive frequency filter                                                                                                                                  | 1 |

|   | 7.4 Adapt  | ive filter properties exploration                                                                                                                     | 1 |

|   |            |                                                                                                                                                       |   |

. . . . . .

| Сс | onten           | ts 🛛    | • • • • • • • • • • • • • • • • • • • •           |    |  |  |  |

|----|-----------------|---------|---------------------------------------------------|----|--|--|--|

|    | 7.5             | Summ    | ary                                               | 82 |  |  |  |

| 8  | Bib             | liograp | bhy                                               | 83 |  |  |  |

| 9  | $\mathbf{List}$ | of au   | thor's publications                               | 93 |  |  |  |

|    | 9.1             | Public  | eations related to the topic of the thesis        | 93 |  |  |  |

|    |                 | 9.1.1   | Publications in impacted journals                 | 93 |  |  |  |

|    |                 | 9.1.2   | Publications in conferences indexed in WoS        | 93 |  |  |  |

|    |                 | 9.1.3   | Publications in conference proceedings            | 93 |  |  |  |

|    | 9.2             | Other   | publications unrelated to the topic of the thesis | 94 |  |  |  |

|    | 9.3             | Citati  | on of author's publications                       | 94 |  |  |  |

|    |                 |         |                                                   |    |  |  |  |

Contents

# List of figures

| 4.1  | Symbol of multiplier                                                                                                 | 16 |

|------|----------------------------------------------------------------------------------------------------------------------|----|

| 4.2  | Symbols of activation functions                                                                                      | 16 |

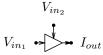

| 4.3  | Symbol of derivation of activation function.                                                                         | 17 |

| 4.4  | Symbol of voltage subtractor.                                                                                        | 18 |

| 4.5  | Formal neuron.                                                                                                       | 19 |

| 4.6  | Analog implementation of forward propagation of a formal neuron.                                                     | 20 |

| 4.7  | Analog implementation of a neural network weight                                                                     | 23 |

| 4.8  | Analog implementation of backpropagation for the output layer.                                                       | 25 |

| 4.9  | Analog implementation of backpropagation between layers                                                              | 27 |

| 4.10 | A fully analog neuron's block implementation including a learning                                                    |    |

|      | circuit with two inputs.                                                                                             | 28 |

| 4.11 | Symbol of an analog neuron with $n$ inputs                                                                           | 29 |

| 4.12 | The block implementation of FAANN with two inputs, three neu-                                                        |    |

|      | rons in the hidden layer, and two outputs                                                                            | 30 |

| 5.1  | Structure of the faann-simulator library.                                                                            | 32 |

| 5.2  | The learning process diagram of the faann-simulator library                                                          | 37 |

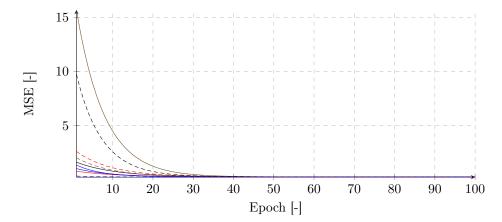

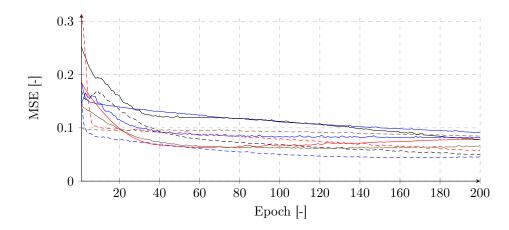

| 5.3  | The learning curve of the FAANN model exported from the faann- $% \left( {{{\rm{T}}_{{\rm{A}}}}_{{\rm{A}}}} \right)$ |    |

|      | simulator                                                                                                            | 38 |

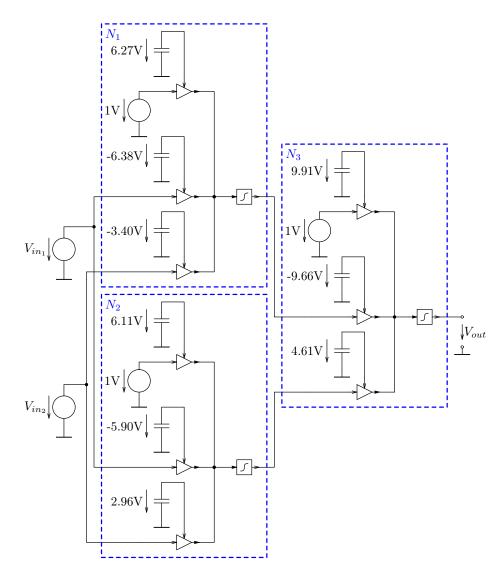

| 5.4  | Schematic of the forward propagation of FAANN in GEEC to                                                             |    |

|      | demonstrate the solution of the XOR problem                                                                          | 39 |

| 5.5  | DC analysis of FAANN for XOR simulation with $V_{in_2} = 1V$                                                         | 41 |

| 5.6  | Weights monitoring in one step of FAANN learning                                                                     | 42 |

| 5.7  | Schematic circuit of a single analog neuron with two inputs for                                                      |    |

|      | learning a dataset using simulation in GEEC                                                                          | 43 |

| 5.8  | Transient simulation of the FAANN learning process with a dataset $% \mathcal{A}^{(n)}$                              |    |

|      | containing two records                                                                                               | 44 |

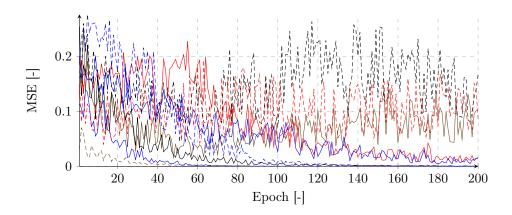

| 5.9  | Transient simulation of the learning process of a FAANN struc-                                                       |    |

|      | ture with a hidden layer                                                                                             | 44 |

| 5.10 | The learning curve of the FAANN model with a small analog                                                            |    |

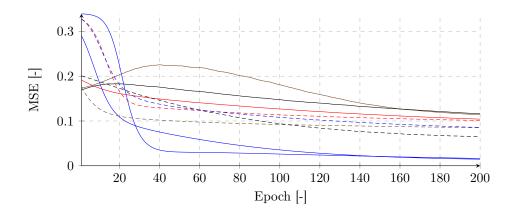

|      | learning rate $(0.1 \text{ V})$ for the XOR problem.                                                                 | 47 |

| 5.11 | The learning curve of the FAANN model with an approximately                                                          |    |

|      | optimal analog learning rate $(0.5 \text{ V})$ for the XOR problem                                                   | 47 |

| 5.12                                      | The learning curve of the FAANN model with a large analog learning rate (0.9 V) for the XOR problem.                                                                                                     | 47       |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

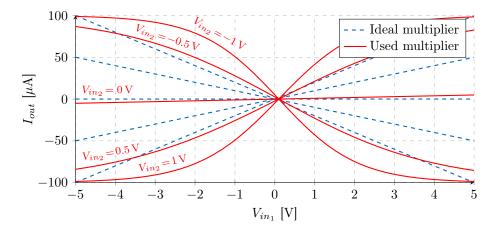

| 5.13                                      | Demonstration of the inaccuracies of the multiplier block used<br>with parasitic properties included                                                                                                     | 48       |

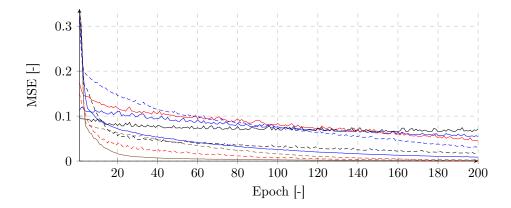

| 5.14                                      | The learning curve of the FAANN model with a modified mul-<br>tiplier block incorporating parasitic properties and with an ap-<br>proximately optimal analog learning rate $(0.5 \text{ V})$ for the XOR | 10       |

| 5.15                                      | problem.       .         The learning curve of the FAANN model with a local minimum         for the XOR problem.                                                                                         | 49<br>50 |

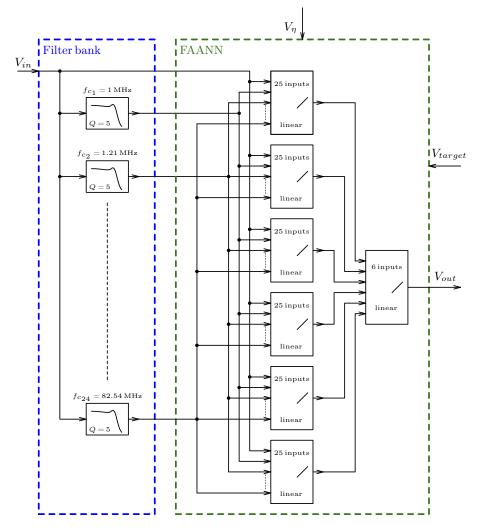

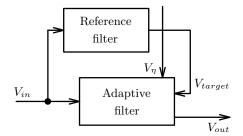

| 6.1                                       | The structure of a proposed simple generic, fully analog adaptive filter for frequencies from 1 MHz to 100 MHz.                                                                                          | 55       |

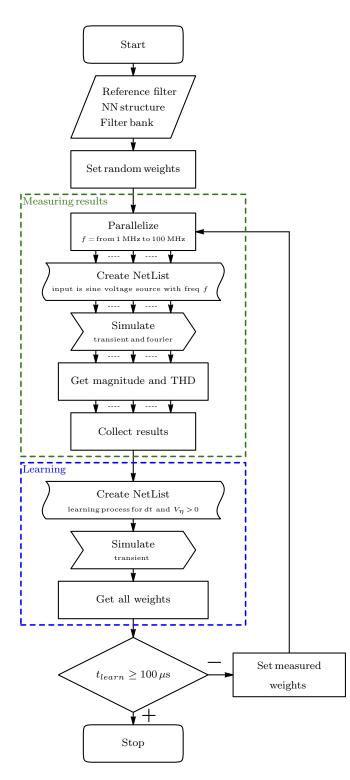

| $\begin{array}{c} 6.2 \\ 6.3 \end{array}$ | Block diagrams used in adaptive filter learning simulations<br>Algorithm flow diagram for the simulation of a fully analog adap-                                                                         | 58       |

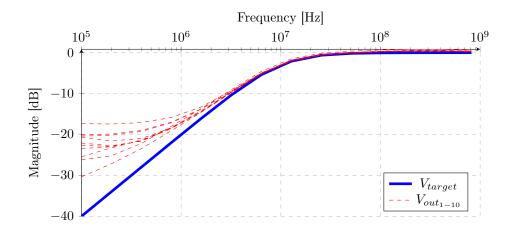

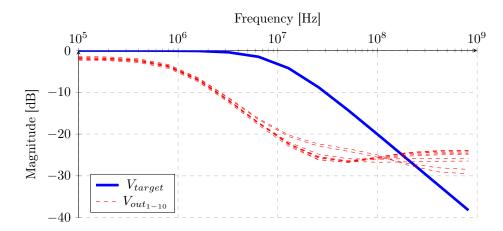

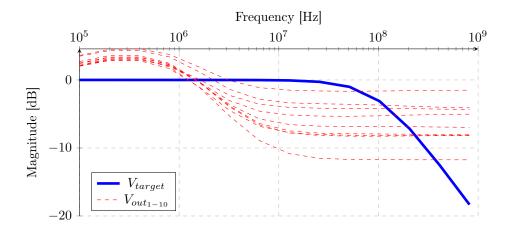

| 6.4                                       | tive filter                                                                                                                                                                                              | 62       |

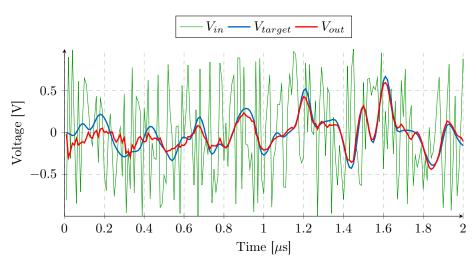

| 6.5                                       | as random noise                                                                                                                                                                                          | 64       |

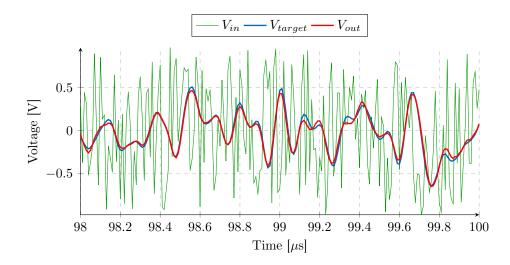

| 6.6                                       | random noise                                                                                                                                                                                             | 64       |

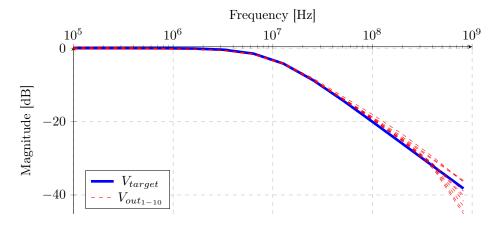

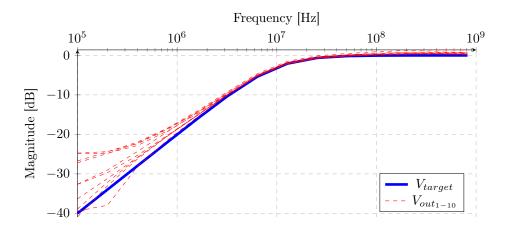

| 6.7                                       | and the reference low-pass filter for ten different learning processes.<br>Comparison of the amplitude characteristics of the adapted filter                                                             | 65       |

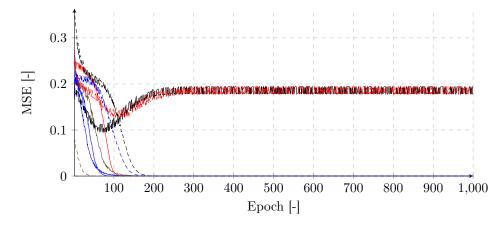

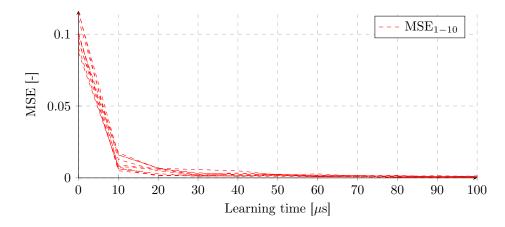

| 6.8                                       | and the reference high-pass filter for ten different learning processes.<br>The learning curve for an adaptive frequency filter using MSE for<br>frequency filter error                                  | 66<br>67 |

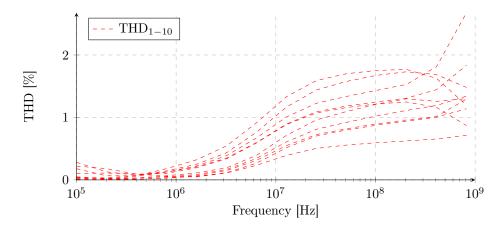

| 6.9                                       | Signal distortion of the learned first-order low-pass filter for ten<br>different learning processes.                                                                                                    | 68       |

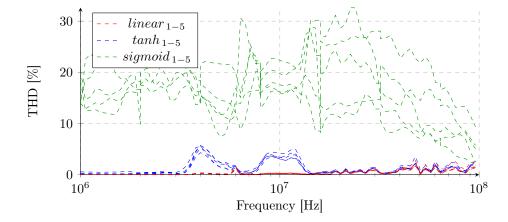

| 6.10                                      | Measured THD of the adapted filter with different activation functions.                                                                                                                                  | 68       |

| 6.11                                      | Comparison of the amplitude characteristics of the adapted filter<br>as a high-pass filter with only low-pass filters in a filter bank for<br>ten different learning processes.                          | 69       |

| 6.12                                      | Comparison of the amplitude characteristics of the adapted filter $(f_c = 100 \text{ MHz})$ with a not fitting filter in the bank (1 MHz and                                                             |          |

| 6.13                                      | 100 MHz) for ten different learning processes Comparison of the amplitude characteristics of the adapted filter $(f_c = 100 \text{ MHz})$ with filters in the bank out of range (1 MHz and               | 70       |

|                                           | 10 MHz) for ten different learning processes                                                                                                                                                             | 71       |

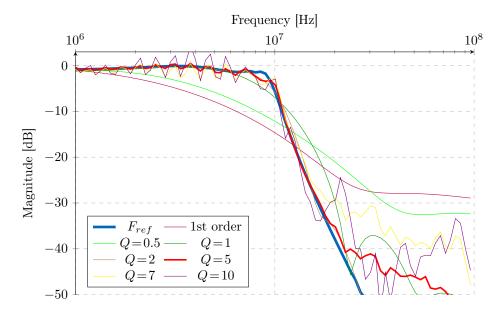

#### List of figures

| 6.14 | Frequency characteristics of adapted filters with different filter            |    |

|------|-------------------------------------------------------------------------------|----|

|      | types in the bank. Filters with defined $Q$ are 2nd order                     | 72 |

| 6.15 | Frequency characteristics of adapted filters with a different num-            |    |

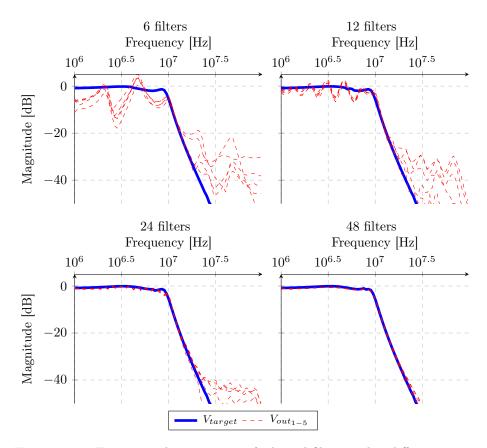

|      | ber of filters in the bank.                                                   | 73 |

| 6.16 | Comparison of frequency characteristics of adapted filters with               |    |

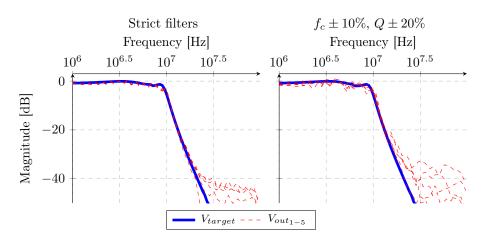

|      | precisely defined filters in the bank versus filters with deviations          |    |

|      | $f_c \pm 10\%$ and $Q \pm 20\%$ in the bank                                   | 74 |

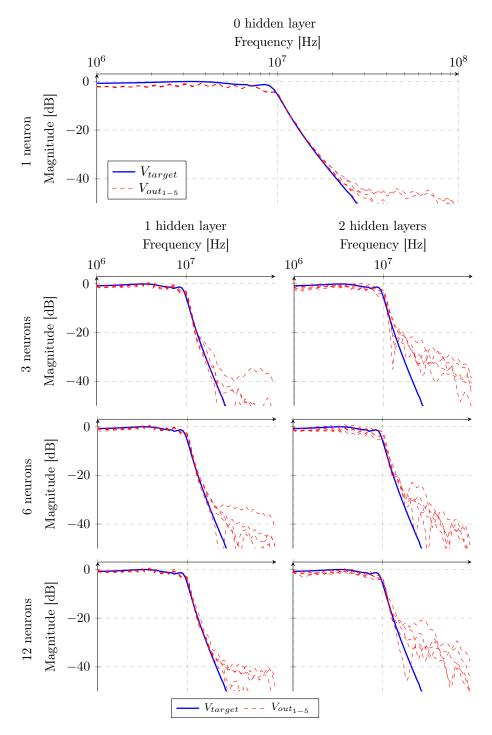

| 6.17 | Frequency characteristics of adapted filters for different FAANN              |    |

|      | structures                                                                    | 75 |

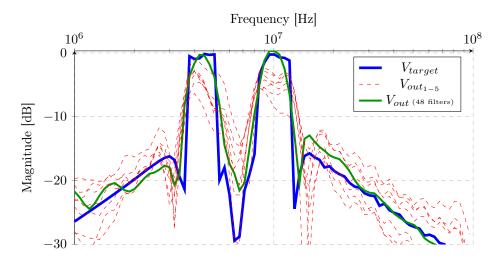

| 6.18 | Frequency characteristics of the adapted filter to dual band-pass             |    |

|      | filter                                                                        | 76 |

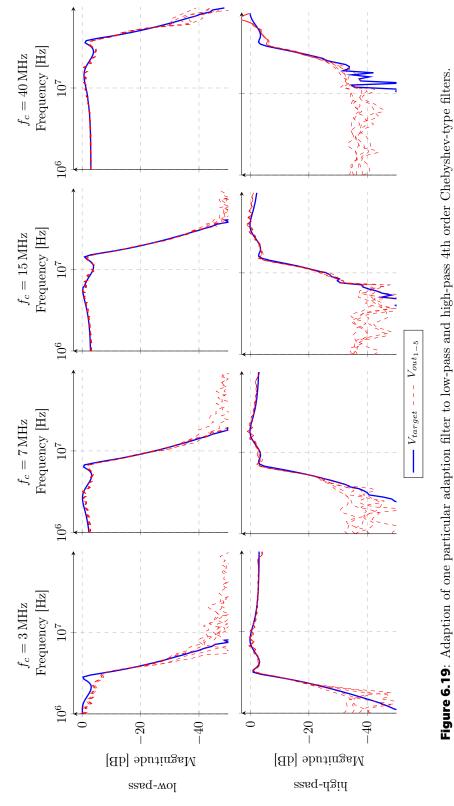

| 6.19 | Adaption of one particular adaption filter to low-pass and high-              |    |

|      | pass 4th order Chebyshev-type filters                                         | 77 |

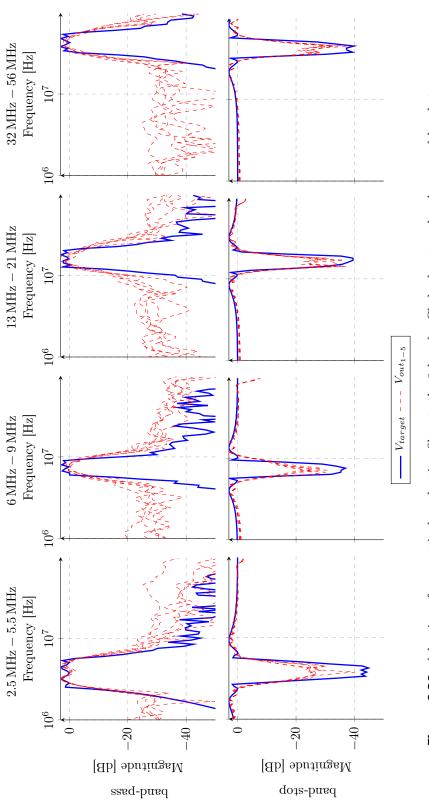

| 6.20 | Adaption of one particular adaption filter to the $8{\rm th}$ order Chebychev | -  |

|      | type band-pass and band-stop.                                                 | 78 |

|      |                                                                               |    |

List of figures

# List of tables

| 5.1 | Comparison of ANN and FAANN outputs for XOR simulation         |    |

|-----|----------------------------------------------------------------|----|

|     | with the same set weights                                      | 40 |

| 5.2 | Neural network weights used to solve the XOR problem           | 40 |

| 5.3 | Dataset for simulation of FAANN with two inputs                | 42 |

| 5.4 | Training dataset of the XOR problem                            | 45 |

| 5.5 | Size of the dataset and structure of neural networks for speed |    |

|     | comparison                                                     | 52 |

| 5.6 | Comparison of time spent on training neural networks in 2021.  | 52 |

List of tables

# List of source codes

| 4.1 | NetList notation of multiplier subcircuit                                  | 16 |

|-----|----------------------------------------------------------------------------|----|

| 4.2 | NetList notation of activation functions                                   | 17 |

| 4.3 | NetList notation of derivative of activation functions                     | 18 |

| 4.4 | NetList notation of subtractor.                                            | 18 |

| 5.1 | A simple example of how to use the faann-simulator library                 | 33 |

| 5.2 | Example of neural network structure definition for faann-simulator.        | 35 |

| 5.3 | Demonstration of manipulating a faann instance and its weights             |    |

|     | with the faann-simulator for possible saving and loading of the            |    |

|     | model                                                                      | 36 |

| 5.4 | Voltage sources definition for circuit in Figure 5.7                       | 43 |

| 6.1 | An example of filter definition in the FAANN input layer in the            |    |

|     | faann-simulator library.                                                   | 57 |

| 6.2 | List filter definition types in the FAANN input layer in the faann-        |    |

|     | simulator library                                                          | 57 |

| 6.3 | A function converts a second-order low-pass filter's cutoff fre-           |    |

|     | quency and quality factor to $ngspice notation $                           | 58 |

| 6.4 | Demonstration of FAANN training and prediction using analog                |    |

|     | signals with the faann-simulator library. $\ldots$ . $\ldots$ . $\ldots$ . | 59 |

| 6.5 | List of input source definition types for training with the faann-         |    |

|     | simulator library                                                          | 60 |

| 6.6 | An example of a target circuit defined as a transfer function for          |    |

|     | a fourth-order low-pass Chebyshev filter with a faann-simulator            |    |

|     | library                                                                    | 61 |

| 6.7 | NetList notation for random noise as a voltage source for ngspice.         | 63 |

| 6.8 | NetList notation for Fourier analysis with THD output for ngspice.         | 67 |

|     |                                                                            |    |

List of source codes

# List of acronyms

- AANN Analog Artificial Neural Network

- **AC** Alternating Current

- ADC Analog-to-Digital Converter

- **AI** Artificial Intelligence

- **ANN** Artificial Neural Network

- **API** Application Programming Interface

- **ASIC** Application-Specific Integrated Circuit

- **CLI** Command Line Interface

- **CMOS** Complementary Metal-Oxide-Semiconductor

- **CNN** Convolutional Neural Network

- CPU Central Processing Unit

- DAC Digital-to-Analog Converter

- **DC** Direct Current

- **EEG** Electroencephalography

- EMG Electromyography

- ${\tt EWC}$  Elastic Weight Consolidation

- FAANN Fully Analog Artificial Neural Network

- **FNN** Feedforward Neural Network

- FPGA Field-Programmable Gate Array

- **GEEC** Graphic Editor of Electrical Circuits

- GPT Generative Pre-trained Transformer

- **GPU** Graphics Processing Unit

List of acronyms

- **GUI** Graphical User Interface

- **IoT** Internet of Things

- JSON JavaScript Object Notation

- $\tt LMS$  Least Mean Squares

- LSTM Long Short-Term Memory

- **MSE** Mean Squared Error

- **NAS** Neural Architecture Search

- **OP** Operating Point

- **PCM** Phase-Change Memory

- **PPG** Photoplethysmography

- ${\tt QNN}\,$  Quantum Neural Network

- Q Quality factor

- **RAM** Random Access Memory

- **RNN** Recurrent Neural Network

- **ReRAM** Resistive Random-Access Memory

- SGD Stochastic Gradient Descent

- **SNN** Spiking Neural Network

- **THD** Total Harmonic Distortion

- **TPU** Tensor Processing Unit

- **VDSL** Very high-speed Digital Subscriber Line

### Chapter 1 Introduction

Artificial Neural Networks (ANNs) have been created based on biological neural networks in the human brain. The concept of artificial neural networks originated in the mid-20th century when scientists such as Warren McCulloch and Walter Pitts investigated the way neural networks work in the brain. In 1943, they published a paper titled "A logical calculus of the ideas immanent in nervous activity", in which they described the essential functions of biological neurons and proposed a model of an artificial neuron [1]. This model became the basis for the development of artificial neural networks.

In the 1950s and 1960s, research on artificial neural networks continued to develop, and the first neural network learning algorithms were developed [2]. However, the limited computing power of computers at the time hampered the development of these networks [3]. In the 1980s, research on artificial neural networks intensified due to advances in parallel computing and the development of new learning algorithms [4]. The first commercial applications of artificial neural networks were also developed at this time, for example, for handwriting recognition and fraud detection [5]. In the 1990s, research on artificial neural networks slowed down as these networks proved to have several limitations, such as slow convergence, susceptibility to overtraining, and inability to explain results [6]. In recent years, research on artificial neural networks have been shown to have great potential for solving complex tasks such as image recognition [7], natural language [8, 9], and driving autonomous vehicles [10].

Therefore, an artificial neural network is a mathematical model inspired by biological neurons used to solve various machine-learning problems, especially for regression and classification tasks [11, 12]. This mathematical model consists of units called "artificial neurons" that are connected by weighted connections. Each artificial neuron receives input data, which is weighted and passed to an activation function that computes the output of the neuron. The neuron's output is then passed on to other neurons as input, or it is an output of the entire neural network. The learning of this neural network is based on changing the weights. These are adjusted by various algorithms so that the network output corresponds to the desired output and thus achieves the correct interpretation of the input data [12, 13, 14].

Artificial neural networks are used in many different fields, such as:

- Image processing: classification, segmenting, and recognizing objects in an image [7, 15].

- Speech processing: speech recognition and speech synthesis [16].

- Language translation: machine translation, multilingual translation, contextual understanding, domain-specific translation [9, 17].

- Fraud detection: detecting fraudulent transactions and identifying criminals [18].

- Driving autonomous vehicles: detecting obstacles on the road and plan the best route for travel [10].

- Financial market forecasting: predicting the prices of stocks and other financial instruments [19].

- Weather forecasting: more accurate weather forecasts and warnings of extreme weather conditions [20].

- Robotics: controlling industrial robots and creating robotic prostheses [21].

- Medicine: analysis of medical images, diagnosing diseases, the detection of drug interactions, developing new drugs, or for personalized medicine [22, 23].

Due to their impressive results, ANNs are gaining popularity. They are being used to solve an increasing number of complex problems and are expected to play an increasingly important role in various aspects of our lives [11, 17].

At the same time, more and more different types of ANNs are being developed, differing in their architecture, each with its specific characteristics and applications [11, 20, 24, 25]. Here are some of the most well-known types of artificial neural networks and their focus:

- Perceptron: One of the simplest neural networks used for binary data classification. Its architecture consists of only one neuron [2].

- Feedforward Neural Network (FNN): The most basic and most widely used type of neural network. It is also known as a unidirectional neural network. The model consists of one input layer, one or more hidden layers, and one output layer [26].

#### 1. Introduction

- Convolutional Neural Network (CNN): Designed to process image data and have the ability to detect and classify objects in an image. It uses convolutional layers that can detect different image patterns [15, 27, 28, 9].

- Recurrent Neural Network (RNN): Designed to process data sequences such as text or audio. It has the ability to retain state over time and is used, for example, for prediction, text generation, or speech recognition [29, 19, 20].

- Autoencoder: Designed for learning compact representations of input data. It is used, for example, for data dimensionality reduction, image recognition, text translation, or data analysis [30, 31].

Almost all modern ANNs are computed based on the von Neumann architecture, which allows efficient implementation of algorithms for a wide range of problems. In this architecture, the computer's memory is used to store both data and instructions while the Central Processing Unit (CPU) fetches them sequentially. The speed of accessing data and instructions is limited by memory bandwidth and memory bus speed, which leads to inefficiency and performance limitations because the CPU spends a significant amount of time waiting for data and instructions. This phenomenon is known as the "von Neumann bottleneck" [32, 33, 34]. Therefore, in recent years, increasing attention has been paid to developing hardware implementations of ANNs that are able to perform computations faster and more efficiently than conventional CPUs [35, 36, 37].

One approach is the use of Graphics Processing Units (GPUs), which are specialized processors designed for graphics processing, but can also be used for training and testing neural networks. GPUs are capable of parallel computation and have greater computational capacity than CPUs, allowing larger complex networks to be trained and tested. They can achieve speed-ups in the teens, but they are not regarded as cost-effective [27, 28].

Another approach is to use specialized chips developed for computing tensors, Tensor Processing Units (TPUs), which are the cornerstone of ANNs. TPUs feature high-speed and energy efficiency, which can be up to 15 times faster than conventional GPUs and consume up to 30 times less power. The TPU architecture is designed to enable efficient real-time forward processing of large datasets [38, 36]. Similar chips can already be found in today's mobile phones used for image and voice processing. Similarly, specialized Field-Programmable Gate Arrays (FPGAs) are in the pipeline, which are programmable circuits that can be used to create specialized hardware architectures for neural networks [24].

However, as the popularity of ANNs grows, so does the scale and complexity of the problems, leading to an increase in the size of the ANNs needed to solve them [12, 15]. The size of networks is directly related to the computation time and energy consumed, which becomes a limiting factor for their real-time applications [39]. It is especially problematic for ANN problems involving concept drift, which is a phenomenon that describes a change in the distribution of data over time. Many factors, such as environmental changes, sensor degradation, user preferences change, or new technology developments, can cause concept drift [40, 41, 42]. If the distribution of data changes so much that the machine learning model is no longer able to accurately predict outputs for the new data, the model becomes invalid [43]. These problems occur, for example, in Internet of Things (IoT), real-time image recognition, and antenna signal processing.

Developers are working on creating specialized chips to address these problems. These chips, called Application-Specific Integrated Circuits (ASICs), are designed for specific applications. Neural networks done by ASICs offer much faster and more power-efficient performance compared to FPGAs, but they are more expensive to develop and manufacture [37]. These specialized chips often operate using a continuous signal, further increasing computation speed and reducing power consumption; such are known as Analog Artificial Neural Networks (AANNs) [34, 44]. However, the actual training of the models loaded onto these devices is primarily done using the traditional von Neumann architecture, as mentioned earlier.

The exception is often found in highly specialized neuromorphic computing. The aim is to develop efficient hardware and software systems that can process information, learn, and adapt, much like biological neural systems. Neuromorphic systems frequently employ specialized architectures and components for complex tasks, delivering high efficiency and low power consumption. These systems can consist of both analog and digital elements. They utilize circuits or processors specifically designed to mimic biological neurons and synapses, creating artificial neural networks for data processing, decision-making, and learning [45, 46, 47, 48].

The increasing use of the IoT and the necessity to process signals from more complex sensors like microphones, cameras, or antennas drives the development of edge computing architectures near sensors [49, 50, 51]. The significant computational power in this area motivates the design of hardware capable of analyzing data from nearby sensors without being affected by the von Neumann bottleneck. This is where analog artificial neural networks come into play, as they are not highly specialized and can process data in real-time with low power consumption. Training these networks requires a learning algorithm such as backpropagation using gradient descent [14] to implement real-time training hardware. However, a fully analog training process based on the backpropagation learning algorithm is still not fully developed and is still an open problem [52, 53].

By incorporating an analog learning algorithm, it becomes possible to transition from standalone software or FPGA units to an on-chip analog train-

#### 1. Introduction

ing implementation, resulting in a fully hardware-based artificial neural network. While this may decrease the flexibility of the structure, it also provides a significant acceleration in the training process of the artificial neural network [33, 44, 48, 54].

Many on-chip learning process designs for both neuromorphic systems and analog neural networks rely on clock control. This approach enables a more flexible structure but slows down the learning process or makes it impossible to process unsampled signals directly from analog sensors [50, 51]. Embracing a fully analog learning process offers several benefits. First, it reduces the need for data conversion between analog and digital domains, saving time and energy. Second, an analog implementation allows continuous learning directly from analog sensor data, facilitating real-time adaptation of the concept drift in real-time applications. Lastly, fully analog learning leads to fully parallel signal processing, yielding significant speed-up and power savings compared to digital implementations.

For the above reasons, this dissertation presents and verifies a new concept of a Fully Analog Artificial Neural Network (FAANN) that implements a circuitbased solution for training an artificial neural network. The proposed concept is inspired by the backpropagation algorithm and is based on gradient descent. The goal is to develop a hardware ANN that can effectively address the limitations of the von Neumann architecture and avoids synchronization signals, making the concept fully analog and fully parallel. It significantly improves computation speed, power consumption, and real-time usability for tasks such as IoT applications, image processing, and high-frequency signal control. 1. Introduction

# Chapter 2 Objectives of the dissertation

This dissertation focuses on addressing several objectives to develop and validate a novel concept for processing signals from various electronic sensors.

- 1. The primary objective is to design a new Fully Analog Artificial Neural Network (FAANN) concept for processing signals from an array of different electronic sensors. This concept should bypass von Neumann's Bottleneck and avoid any synchronization signals, enabling real-time learning capabilities.

- 2. The next objective is to validate the functionality of the proposed structure by analysis through an electrical behavioral model. It should ensure that the proposed structure will be able to learn and with sufficient speed. Additionally, it will analyze the fundamental behavior of this concept and compare it to traditional ANN approaches.

- 3. Another objective is to explore the practical applications of the FAANN system by utilizing it to develop an adaptive frequency filter. The adaptive filter should be designed to operate at higher frequencies to show the potential of FAANN.

- 4. The final objective is to verify the functionality of the designed adaptive filter concept, which is based on FAANN, through additional simulations, particularly considering their configurability and adaptability. These simulations should describe the fundamental advantages and disadvantages.

7

2. Objectives of the dissertation

# Chapter 3 State of the art

Nowadays, Artificial Neural Networks (ANNs) have become a crucial part of many diverse fields due to their ability to learn, adapt, and solve complex problems. They are designed to mimic the functioning of the human brain, which consists of interconnected processing nodes, also known as neurons [11].

A significant development in recent years has been the advent of deep learning, a subset of machine learning that utilizes ANNs with many hidden layers [7, 9, 16, 21, 35]. Specifically, Convolutional Neural Networks (CNNs) have triggered image and video processing breakthroughs. These networks use convolutional layers to extract features from images and videos more efficiently than traditional methods [15, 34, 55, 56].

A promising area is the development of capsule networks, a concept introduced as an alternative to CNNs [31]. These networks are capable of processing spatial relationships between objects in an image, potentially surpassing some of the limitations of CNNs. Although still in the experimental stage, they could possibly bring about a revolution in image recognition tasks [57].

On the other hand, Recurrent Neural Network (RNN) and Long Short-Term Memory (LSTM) have proven to be exceptionally promising for sequence prediction problems, such as natural language processing or time series prediction [8, 58]. These networks have an internal state that allows them to remember previous inputs in the current decision-making process. Thanks to their ability to handle time-dynamic behavior, RNN, and LSTM have become key in sequence-based tasks [29]. Examples of RNN and LSTM usage include weather forecasting and even stock price prediction [19, 20].

A significant milestone in the field of ANNs is the emergence of transformers. Unlike traditional RNNs or CNNs, transformers rely solely on self-attention mechanisms to capture dependencies between different positions in a sequence. This attention mechanism allows transformers to efficiently process long-range dependencies and contextual information without needing sequential processing, making them highly parallelizable and faster to train [59, 60].

Transformers have paved the way for novel architectures such as the Generative

Pre-trained Transformer (GPT) models, widely used for text generation tasks [17]. GPT-4, so far the largest model in the series, has demonstrated impressive language generation capabilities, producing coherent and contextually relevant text across a wide range of prompts. It is currently being explored for various applications, such as its benefits and risks for medical applications [22].

With the arrival of quantum computers, Quantum Neural Networks (QNNs) have emerged as a potential future direction for ANNs. QNNs leverage quantum phenomena to enhance the speed and capacity of traditional neural networks. Although they are only in the initial phase, they could lead to significant progress in this field, but substantial issues persist regarding hardware stability and error correction [25, 61, 62].

ANNs have several advantages that make them suitable for many machinelearning tasks [11]. Some of these include:

- Noise processing: ANNs are highly robust and can handle noise in input data. It makes them suitable for real-world situations where data may not be clean or may contain errors [12, 14].

- Nonlinearity: ANNs are capable of modeling complex nonlinear relationships, which can be critical in many real-world applications where relationships between variables are not straightforward [63].

- Generalization: After training, ANNs can generalize learned examples to new ones. This ability makes them useful for image recognition or natural language processing tasks [7, 8].

Despite remarkable progress, there are still persisting issues in the field of ANNs. Some of these include:

- Lack of transparency or the black box problem: It is often difficult to understand how ANNs make their decisions, as this process can be very complex and opaque. This lack of interpretability can be problematic in situations where it is necessary to understand the decision-making process, such as in healthcare or legal environments [64].

- Overfitting: ANNs, particularly deep neural networks, are prone to overfitting, especially when working with a small dataset. Overfitting means that the network may perform well on training data but poorly on new, unseen data [65].

- Architecture design complexity: ANNs are usually complex architectures, and their design requires considerable effort and expertise. This is currently being addressed by Neural Architecture Search (NAS) algorithms, which automate the design of artificial neural networks and represent a

new development in ANN technology. NAS algorithms attempt to create models that outperform human-designed models, which would significantly accelerate the model development process [66].

Training time and computational resources: Training ANNs can require substantial amounts of time and computational resources, especially in the case of large datasets or complex architectures. Therefore, they are less suitable for smaller projects or organizations with limited computational resources [32, 43, 59, 60, 67].

Consequently, much recent research is focused on addressing these problems. For example, various techniques such as quantization, compression, and acceleration are being explored in the area of computational resources [35, 68, 69].

Neural network accelerators have recently become a central focus of hardware development that facilitates the computational demands of ANNs. These specialized hardware accelerators, designed to speed up the execution of neural network tasks, have significantly increased the speed and efficiency of training and deploying ANNs [33, 35, 70].

Field-Programmable Gate Arrays (FPGAs) and Application-Specific Integrated Circuits (ASICs) are two types of neural network accelerators widely used due to their efficient energy use and high-performance capabilities. FPGAs provide a flexible architecture that allows for reprogramming the hardware best to suit the specific needs of a neural network model. On the other hand, ASICs are specifically designed for specific tasks, leading to significantly higher performance compared to more general hardware. However, ASICs lack the flexibility of FPGAs as they cannot be reprogrammed after production [24, 37].

Graphics Processing Units (GPUs) also play an important role in accelerating neural networks, thanks to their highly parallel structure suitable for matrix and vector operations used in ANNs. Graphics processors, originally designed to accelerate computer graphics, have now found widespread use in the field of Artificial Intelligence (AI). At the forefront of this shift are GPUs from companies like NVIDIA, whose CUDA software platform has made it easier for developers to utilize the parallel computing power of GPUs [27, 28, 37].

Another example of a specialized neural network accelerator is the Tensor Processing Unit (TPU). TPUs are Google's custom-built ASICs specifically designed to accelerate machine learning tasks. They have been optimized for TensorFlow, Google's open-source machine learning framework. With their unique architecture and design, TPUs are able to execute large-scale tensor computations efficiently, resulting in significantly faster processing times for tasks such as training and inference in neural networks [35, 36, 38].

Despite the substantial improvements by neural network accelerators, challenges still exist. Active research areas include energy efficiency, computational power, cost, and the ability to keep up with the rapidly changing environment [40, 43]. Given the pivotal role of neural networks in a wide range of applications, from image recognition to natural language processing, progress in the field of neural network accelerators is expected to continue rapidly in the coming years [35].

Real-time learning in neural networks continues to be a thriving field of research and development, with applications expanding beyond autonomous vehicles, robotic systems, and dynamic recommendation systems. The ability of neural networks to adapt their knowledge on-the-fly, learning from new data as it becomes available, without requiring full retraining, is a cornerstone of modern AI systems [10, 21, 39, 38].

Traditionally, most neural network models are trained on a static dataset and then deployed for inference, with no ability to learn from new data. The learned model is then rendered obsolete and non-valid. However, as the demand for real-time learning capability has grown, so has the suite of methods designed to achieve it [40, 41, 42].

One of the approaches to this is federated learning, where a model is trained across multiple decentralized edge devices, learning from new data as it arrives. This approach not only facilitates real-time learning but also respects the privacy of the data, as the raw data does not need to leave the device. It has proven particularly useful in applications like personalized recommendation systems and healthcare analytics, where data privacy is paramount [71].

Transfer learning is another technique that bolsters real-time learning, where a pre-trained model is used and fine-tuned for a different but related task. This approach can expedite the learning process, especially in real-time scenarios where a model can leverage prior knowledge to make better predictions or decisions. It is especially prevalent in natural language processing tasks and image classification problems [72].

Ensemble learning is another way to enhance real-time learning. In this approach, multiple models or versions of a model contribute to the final prediction. It can increase the robustness and generalizability of the model, making it better-equipped to handle the dynamic nature of real-time data [73].

Continuous learning, also known as lifelong learning or incremental learning, is an approach in machine learning where models are designed to acquire new knowledge, adapt to changing data, and improve their performance over time [74]. It addresses the issue of catastrophic forgetting, which occurs when a neural network learns new tasks and forgets how to perform previously learned tasks. Techniques like Elastic Weight Consolidation (EWC) have shown promise in mitigating this issue, allowing the neural network to learn new tasks in realtime without forgetting the old ones [75].

With the beginning of edge computing and IoT, the need for lightweight

real-time learning models that can operate on devices with limited computational resources is increasing [49, 50, 51]. To this end, various techniques are being explored, such as model quantization, knowledge distillation, and the development of compact neural network architectures like MobileNet [55] and EfficientNet [56]. Another promising direction is the application of TinyML, which specializes in deploying machine learning capabilities on embedded systems, further driving the feasibility of real-time learning in resource-constrained environments [76].

One of the answers to this challenge is the growing research of Analog Artificial Neural Networks (AANNs) and also neuromorphic computing systems, which present a promising trend in the hardware for machine learning. These systems use physical, electrical circuits to mimic the behavior of neurons and synapses, the basic units of biological brains. These circuits, crafted with advanced semiconductor technologies, enable simultaneous data storage and analog computation, potentially significantly improving energy efficiency and speed of machine learning operations [45, 77, 78].

Several key advancements have been made in this field. Notably, neuromorphic computing chips like IBM's TrueNorth [70] and Intel's Loihi [45] have gained recognition. These chips contain Spiking Neural Networks (SNNs), which more closely resemble the activity of biological neurons compared to traditional artificial neural networks. This allows these systems to process data in a highly parallel and energy-efficient manner, enabling more powerful and compact artificial intelligence systems [79].

Another significant advancement in analog neural networks is the emergence of memristors, electronic components which behave as a variable resistance whose value depends on the amount of electric charge flowing through it. Memristors can be used to construct analog weight elements for AANNs, effectively implementing synapse connections in a neuromorphic system. This allows data storage and manipulation in the same place, thereby reducing data movement and improving energy efficiency [44, 46, 50, 53, 77].

While significant progress has been made in the area of AANNs and neuromorphic systems, there are still challenges to overcome. One of the main challenges is the analog implementation of learning algorithms. Most current neuromorphic systems use classic digital training algorithms based on gradient descent, which are computationally and memory intensive. Research in this area focuses on developing new algorithms suitable for analog implementations that use the natural physical properties of electronic devices to perform mathematical operations [47, 53, 79].

Analog circuits have been used to implement various learning algorithms, such as backpropagation and Hebbian learning [53, 80]. In backpropagationbased systems, weights are usually stored in digital memory and converted to analog signals during computation. However, new analog memory devices, such as Phase-Change Memory (PCM) and Resistive Random-Access Memory (ReRAM), have been used to store weights directly in analog form, leading to more efficient learning systems [34, 35].

However, the analog implementation of learning neural networks is not without challenges. Analog devices suffer from issues such as device variability, nonlinearity, and noise, which can lead to inaccurate computations. Moreover, integrating analog devices with digital systems presents substantial challenges. As the technology matures and more robust designs and error correction methods are developed, these obstacles are expected to be overcome, paving the way for the widespread use of analog neural networks in real-world applications. It can cause a shift from the traditional digital-centric AI approach to one that combines digital and analog computation, potentially leading to more powerful, energy-efficient, compact AI systems, and efficient on-device machine learning applications [55, 56, 77, 70].

Despite the advancements achieved thus far, real-time learning of neural networks still faces significant challenges too. Striking a balance between stability and flexibility, computational power and memory constraints, as well as privacy and data security issues, are subjects of ongoing research. Nevertheless, considering the escalating demand for real-time learning capabilities across many applications, substantial progress in this realm is anticipated in the years to come [37, 39, 71].

In conclusion, though still an expeditiously evolving field, analog neural networks, and neuromorphic systems hint at a new generation of AI hardware. Such systems could potentially revolutionize the machine learning domain and provide notable improvements in energy efficiency and speed compared to traditional digital systems. The ongoing research lays a base for more robust and efficient artificial intelligence systems in the future. The rapid progress in this field suggests more exciting developments in the coming years with potential impacts across various sectors [7, 10, 11, 21, 22, 51].

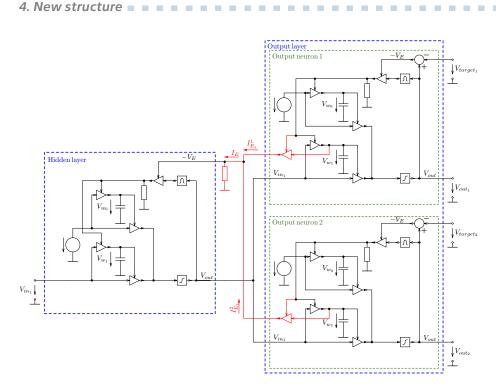

# Chapter 4 New structure

This chapter introduces a novel concept for Fully Analog Artificial Neural Networks (FAANNs) [52], specifically designed to meet certain criteria. The network is configured to process various signals from a diverse array of electronic sensors. These include basic sensors that measure temperature, light intensity, and electrical conductivity, as well as more complex sensors such as microphones, cameras, or antennas. Another criterion is to enhance measurement accuracy by accounting for sensor degradation and changing environmental conditions, a phenomenon known as concept drift [40]. Additionally, the FAANN is designed to infer unmeasured quantities dependent on the measured ones. It is an important characteristic when the quantity of interest is costly or time-consuming to measure directly.

These requirements led to the design of FAANNs to be used for real-time learning, even for high-speed applications. The acceleration of the neural network's training process in this research is grounded on several principles. These allow it to effectively bypass the limitations of the von Neumann architecture [32], avoid synchronization signals, clock control, and overcome constraints related to sampling, Analog-to-Digital Converter (ADC) and Digital-to-Analog Converter (DAC).

The novel concept of FAANNs introduces a circuit-based solution for training artificial neural networks. This innovative concept is inspired by the backpropagation algorithm and is built on the principles of gradient descent [14], aiming to establish a hardware-based training process. The training process is executed through feedback from an analog electrical circuit, making the entire operation fully analog. This approach also eliminates the need for any clock control that could slow down signal propagation, thereby allowing the neural network to work fully parallel [44, 53, 54].

The newly designed structure aims to maximize versatility, potentially accommodating as many types of neural networks as possible. Therefore, it is designed as a feedforward neural network, serving as the foundation for creating various neural network types, all consisting of identical cells.

# 4.1 Blocks

When constructing a FAANN, it is essential to include several components, often referred to as "blocks". These blocks help describe the neural network's design process more straightforwardly and clearly.

The electrical implementation of these blocks can be achieved using various analog components, such as operational amplifiers, transistors, and resistors. However, for verifying the functionality of this concept, which is the objective of this dissertation, these blocks are temporarily considered ideal for the sake of simplicity.

In this section, each of these blocks is represented with a schematic symbol, mathematical descriptions, and NetList notations for subsequent simulation.

#### 4.1.1 Multiplier

Figure 4.1: Symbol of multiplier.

The multiplier block has the schematic symbol shown in Figure 4.1. It is a function that multiplies two voltages and whose output is a current calculated by

$$I_{out} = K_m \cdot V_{in_1} \cdot V_{in_2},\tag{4.1}$$

where  $K_m$  [A/V<sup>2</sup>] is the ratio of output to the product of inputs.

The NetList notation of this block used in simulations is shown in Code 4.1.

1 .subckt multiplier in1 in2 out

2 B1 0 out I=0.0005\*v(in1)\*v(in2)

3 .ends multiplier

Code 4.1: NetList notation of multiplier subcircuit.

#### 4.1.2 Activation function

| $I_{in} \bullet \checkmark \bullet V_{out}$ | $I_{in} \twoheadrightarrow \mathcal{I} \twoheadrightarrow V_{out}$ |

|---------------------------------------------|--------------------------------------------------------------------|

| (a) Linear.                                 | (b) Nonlinear.                                                     |

Figure 4.2: Symbols of activation functions.

The blocks representing an activation function have the schematic symbols shown in Figure 4.2. The most commonly used activation function is a sigmoid [12], which is described by

$$V_{out} = \frac{V_{amp}}{1 + e^{-\frac{I_{in}}{I_{ref}}}},\tag{4.2}$$

where  $V_{amp}$  is a constant determining the maximum possible voltage and  $I_{ref}$  is a referential current.

The notations for three distinct activation functions used in simulations, namely the sigmoid, hyperbolic tangent, and linear identity activation functions, are depicted in the NetList language in Code 4.2. Some of these activation functions exhibit nonlinearity in their formulation. This nonlinear behavior can be attributed to two factors. The first relates to the restrictions by voltage constraints, which influence the current traversing the system. Secondly, this nonlinearity has characteristics of the blocks nearer to their real implementation [54].

```

.subckt activationFunctionSigmoid in out

1

B1 out 0 V=1/(1+exp(-v(in)*5))

2

.ends activationFunctionSigmoid

3

4

\mathbf{5}

.subckt activationFunctionTanh in out

6

B1 out 0 V=tanh(v(in)*2)

7

.ends activationFunctionTanh

8

.subckt activationFunctionIdentity in out

9

10

B1 out 0 V=5*tanh(v(in)/5)

.ends activationFunctionIdentity

11

```

Code 4.2: NetList notation of activation functions.

#### 4.1.3 Derivative of an activation function

$$V_{in} \rightarrow \bigwedge V_{out}$$

The block representing the derivative of an activation function has the schematic symbol shown in Figure 4.3. In the case of the sigmoid activation function, the block is described by

$$V_{out} = K_m \frac{e^{\frac{V_{in}}{V_{ref}}}}{(e^{\frac{V_{in}}{V_{ref}}} + 1)^2},$$

(4.3)

where  $K_m$  is a proportionality voltage constant and  $V_{ref}$  is a referential voltage.

The NetList notation for the three different derivations of the activation function that are used in the simulations are shown in Code 4.3. These are specifically the derivatives of the nonlinear sigmoid, tangent hyperbolic, and linear identity activation functions.

```

1

.subckt diffActivationFunctionSigmoid in out

\mathbf{2}

B1 out 0 V=4*exp(v(in)*5)/((exp(v(in)*5)+1)^2)

3

.ends diffActivationFunctionSigmoid

4

5

.subckt diffActivationFunctionTanh in out

6

B1 out 0 V=2/(cosh(4*v(in))+1)

7

.ends diffActivationFunctionTanh

8

9

.subckt diffActivationFunctionIdentity in out

10

B1 out 0 V=1

.ends diffActivationFunctionIdentity

11

```

#### 4.1.4 Subtractor

Figure 4.4: Symbol of voltage subtractor.

The subtractor block has the schematic symbol shown in Figure 4.4. It is a function that subtracts two voltages and whose output is calculated by

$$V_{out} = V_{in_1} - V_{in_2}.$$

(4.4)

The NetList notation of this block used in simulations is shown in Code 4.4.

```

1 .subckt subtractor in1 in2 out

2 B1 out 0 V=v(in1)-v(in2)

3 .ends subtractor

```

Code 4.4: NetList notation of subtractor.

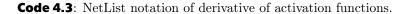

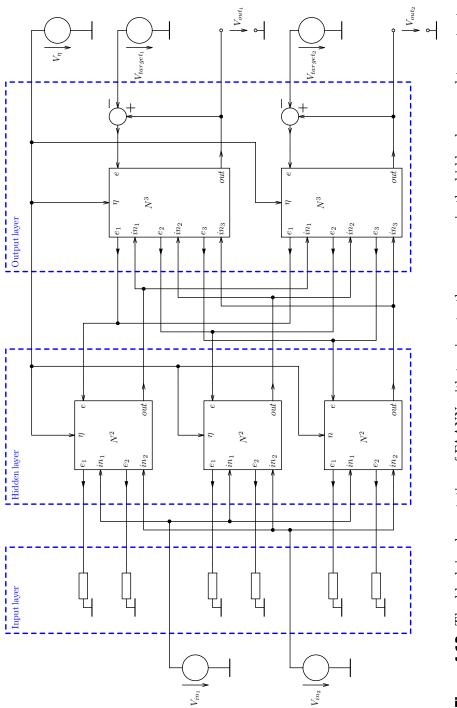

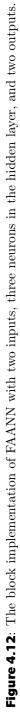

### 4.2 Forward propagation structure

The FAANN comprises forward and backward propagation, two crucial components that will be further discussed. Forward propagation involves processing input data through the neural network layers to produce an output. In contrast, backward propagation focuses on adjusting the network weights based on the output errors [12]. This section describes the design and concept implementation of forward propagation in the FAANN.

The focus is on the forward propagation of the formal neuron, which serves as the foundation for other types of neural networks. A graphical representation

Figure 4.5: Formal neuron.

of this part of the formal neuron is shown in Figure 4.5. In a neural network, forward propagation involves calculating the output of each neuron in the network by applying a set of mathematical operations.

The fundamental equation for the output of a neuron can be expressed as

$$out = S\Big(\sum_{i=0}^{N} w_i i n_i\Big),\tag{4.5}$$

where *out* is the output of the neuron,  $in_i$  represents the input values,  $w_i$  denotes the corresponding weights,  $in_0$  is the bias term, and S is the activation function. This equation captures the core principle of forward propagation, where input values are multiplied by their respective weights, summed up, and adjusted with a bias term before being passed through the activation function to produce the neuron's output [12, 14].

The forward propagation process starts at the input layer and continues through hidden layers until it reaches the output layer. At each layer, the neurons receive input from the previous layer, perform the above calculations, and pass the output to the next layer. The choice of activation function Sis critical in introducing nonlinearity into the network, allowing it to model complex relationships between inputs and outputs [14].

The hardware implementation of forward propagation in neural networks has been a subject of extensive research and development, as it plays a crucial role in the performance of these networks. Numerous studies have explored various approaches to implementing forward propagation in both digital and analog circuits, aiming to optimize speed, energy efficiency, and accuracy [33, 48, 53, 54, 81, 82]. Hardware solutions, such as ASICs, FPGAs, and custom analog circuits, have been employed to execute the complex computations involved in forward propagation. These approaches have made significant strides in reducing the latency and power consumption of neural networks, making them more suitable for real-time applications and near-sensor processing [39, 50]. As a result, hardware implementations of forward propagation continue to advance the state-of-the-art in neural network technology, enabling new possibilities in machine learning, signal processing, and a wide range of applications [33, 35, 53].

Such a formal neuron in analog form has been implemented numerous times in various designs. For this structure, all its parts will be considered as voltage components. This means that the neuron's inputs, weights, and outputs are represented as voltages. The fundamental equation for the output of a voltagebased formal neuron can be expressed as

$$V_{out} = S\left(\sum_{i=0}^{N} V_{w_i} V_{in_i}\right),\tag{4.6}$$

where  $V_{out}$  is the output voltage of the neuron,  $V_{in_i}$  represents the input voltage values,  $V_{w_i}$  denotes the corresponding weight voltages,  $V_{in_0}$  is the bias voltage, and S is the activation function. In this configuration, the neuron performs the calculations using voltage levels rather than numeric values.

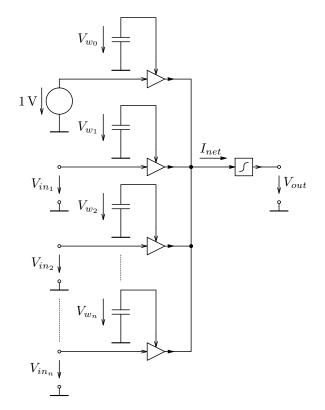

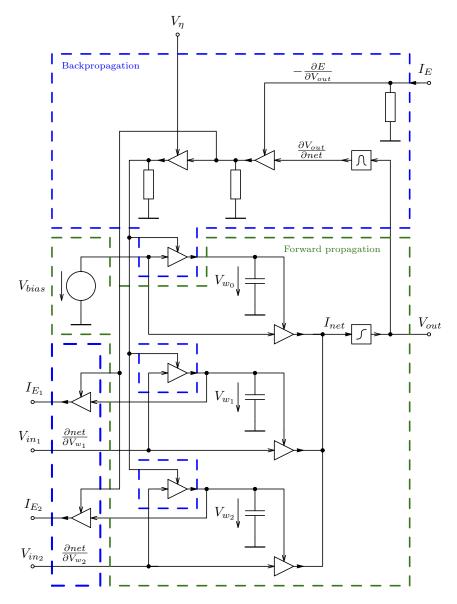

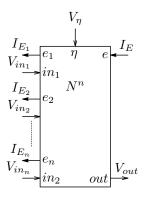

Figure 4.6: Analog implementation of forward propagation of a formal neuron.

The entire behavior of the designed forward propagation of the FAANN is described by Equation (4.6), and the corresponding analog concept design is illustrated in Figure 4.6. The weights  $V_{w_i}$  are represented by voltages stored on capacitors, which will be elaborated in the subsequent section. Each input is connected to a multiplier, where the output is a current determined by Equation (4.1). The sum operation is performed using Kirchhoff's circuit laws at the node preceding the activation function; the resulting current is denoted as  $I_{net}$ . Finally, the activation function is applied to the sum.

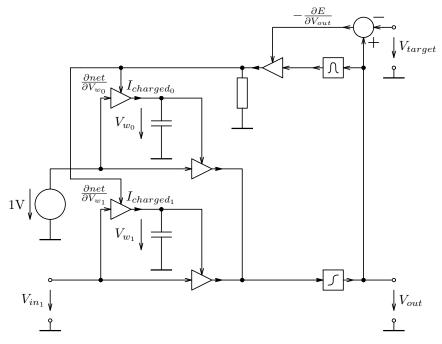

## 4.3 Novel backpropagation structure

The most widely used approach to training artificial neural networks involves a combination of backpropagation and either Stochastic Gradient Descent (SGD) or one of its variations [14]. In the field of machine learning, backpropagation stands out as a crucial algorithm, essential for training not only feedforward neural networks but also any differentiable parameterized networks [12].

Backpropagation is an algorithm that computes the gradient of the loss function with respect to the network's weights  $\frac{\partial E}{\partial w_k}$  for a single pair of inputoutput data. This algorithm leverages the chain rule from calculus, a rule used to compute the derivative of the composition of multiple differentiable functions. This method can be used for multiple weight updates by calculating the gradient of the loss function for each example in the training dataset.

The renowned backpropagation algorithm is commonly combined with the stochastic gradient descent method. In this combination, the weight update is defined by the following equation

$$w_{k+1} = w_k - \eta \frac{\partial E}{\partial w_k},\tag{4.7}$$

where  $w_k$  represents a weight at step k (with  $k \in \mathbb{N}$ , the set of natural numbers), E symbolizes the error, and  $\eta$  denotes the learning rate. This equation defines how the weights of the network should be adjusted to minimize the error between the network's output and the expected output [12].

There are two primary ways of training analog neural networks. The first one employs gradient descent and backpropagation of the error, which is a method also utilized in traditional networks. This process mainly takes place in the digital component of the system and then gets transmitted to the analog part [48]. However, this approach is subject to the von Neumann bottleneck [32].

The second way involves designing systems that replicate the structure and function of the brain, a field sometimes referred to as neuromorphic computing or neuromorphic engineering. This technique deviates from the digital computations performed by conventional artificial neural networks. The training of these networks usually necessitates specialized algorithms based on the physical properties of the used components, and are currently developed only for specific tasks [46].

Regardless, these techniques generally require some form of gradient descent and backpropagation or their approximations, as these are the most effective methods known for training networks. However, the application of these methods on analog hardware can be demanding, and a significant portion of research in this field is dedicated to discovering effective ways to achieve this.

This work introduces a learning method suited for near-sensor applications and capable of functioning in real-time. The method is rooted in backpropagation with SGD, chosen for reasons previously discussed.

Designing this learning process in a completely analog manner presents a significant challenge due to the stepwise nature of the algorithm. As illustrated in Equation (4.7), k represents a step that needs to be bypassed.

To address this challenge, the process is reconstructed within a continuous domain. It is realized by substituting the step variable k with continuous time t, and integrating the weight w over time. Consequently, the revised formula for weight change appears as

$$w(t) = w(t_0) - \eta \int_{t_0}^t \frac{\partial E(\tau)}{\partial w(\tau)} d\tau, \qquad (4.8)$$

where w(t) denotes the weight function at continuous time  $t \in \mathbb{R}$ , and  $E(\tau)$  represents the error, which is changing continuously over time too.

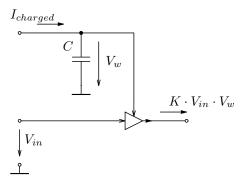

#### 4.3.1 Weights implementation

When designing an analog learning circuit, the selection of the suitable component to store and adjust the "weight" value, a key part of the learning process, is crucial.

Memristors and memristor arrays have recently emerged as a promising solution for this. They store the weight value as a resistance level and are particularly appealing due to their similarity to biological synapses. Additionally, their compactness and low power consumption make them an attractive option [77, 83]. However, this technology is still evolving and needs to be more robust for some applications [53].

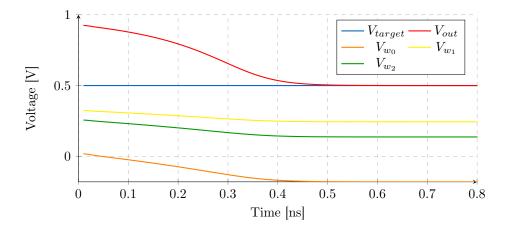

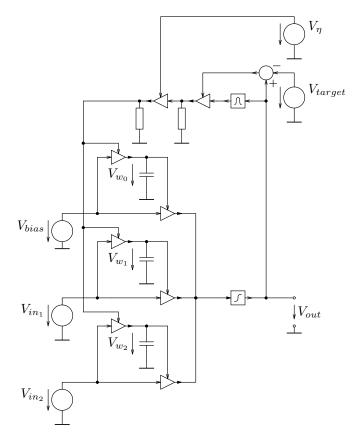

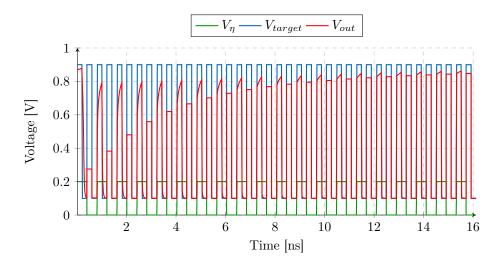

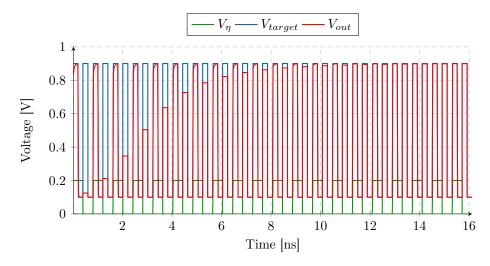

Another choice is to use capacitors for their ability to store charge. They are a proven and robust technology frequently used in integrated circuits. Their ubiquity within these circuits makes them particularly convenient for concept validation, as their functionality is straightforward to demonstrate.